## Sample exam subject

- G.1. Design an 8 bit parallel printer interface connected to an ATmega64 microcontroller (to its ports). The transfer protocol should use 2 handshaking signals: STB output (informing the printer that data is available on the data lines) and BUSY or ACK (input) informing the microcontroller that the printer is either busy or is ready to receive new data. Explain the design. Draw the schematic of the interface. Draw the flow-chart of the procedure that sends a string of characters to the printer. Also write the procedure in assembly language.

- G.2. Explain the principles of the input-caption function available through the AVR timer and comparator.

- G.3. Design an *EPROM* memory interface for a 8086μP (having a 16 bit data bus). Total size: 64 KB, mapped in the lower part of the memory space. Use EPROM chips: 4K x 4 bits. The interface design should contain: the memory chips layout, the address decoder, the data, address and control lines interconnection. Explain the design

- G.4. Explain how are generated the control signals of an 8086 microprocessor in maximum mode.

- G.5. Explain the interrupt response sequence (what happens when an interrupt request occurs).

- G.6. What is the "daisy chain technique" and give 2 examples in which can be used?

The solution is presented in the next pages .....

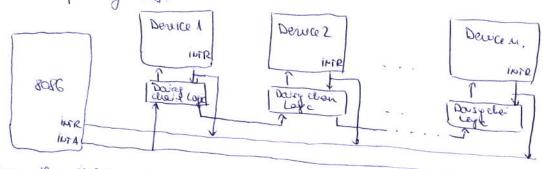

G6. Daisy chaining kellingue is a kellingue to resolve priority conflicts among simultaneous reguests. It consists of the fact that the derices requesting some feartence are put on a choice and the first one to on chain that regrests a feature will have it. It can be used in the following examples:

1. Therupt reguests

Here the INTA signal will have known the daisy chain lagic. The first dervice reguesting interrupt will have the ordnowledge. (i.e. priority is home Device 1 -> derver on decressing)

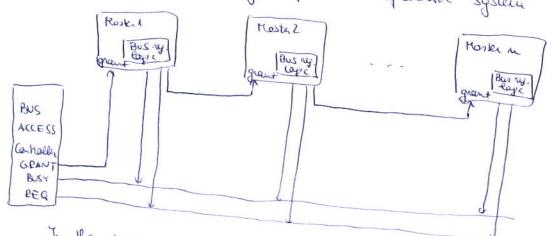

2. Bus request on a loosely compled multiprocessor system

In the same manner as before, requests me asserted on the regrest has, and the access grant will go through all mosters until the first one that is lightesting. Priority is decreasing from Mosteral -> Mostern.

5. The interrupt response requerce will include the following steps:

## 4. There case of POSE

- flags are pushed on the stock

- interrupt and trap flags are cleared ( if and IF In SREO)

- the codesegment address (Cs) and wshuckion points, (dP) are pushed on

- the new CS and iP are set occording to the contents of the inferript vector labb.

INTO has the entry at oddless H\*M. (4 bytes, I for CS and

I for iP).

- the routine is executed

- on return the CS, iP and flags are popped from register. (as flags were purhed before cleaning iF and TF, they do not need to be reset)

## B. In the case of AVR (ATmega64)

- the response takes at least 4 cycles:

- PC is purhed on stock

- jump is made according to interrupt vector table

- interrupt flag is cleared from SREG (CLi)

- if the interrupt is a waterp call, a 4 more cycle is inchadred

- Upon return:

- pop PC Rom stock

- innement stack pointer I (in fact, this is part of a pop)

- re-endré intempts (SEi)

La addition

ch. the contral signols of an POPG microprocessor in maximum made, are generated using a bus controller (PJPP device). In maximum made, 80PG has S2-S0 status bits as outputs. The PJPP tales these outputs, and based on their combinations generates the meeded contral signals. These signals are: iOPC, io WC, HEMPC, MEMWC, AiOPC, AMEMPC, DEN, DTIP, ALE

Nake: the latter for 3 signals are not abrious from their name, so I explain the usage: DEN is the cubble is connected to the evolbe pin of the transcrivers. This will enable data go through them.

DTIE (date transmit (receive) is connected to the direction pine of the transmisures. It indicates up pape transmits or receives date.

ALE - (address lately enoble) - enobles addresses from lately to address bus.

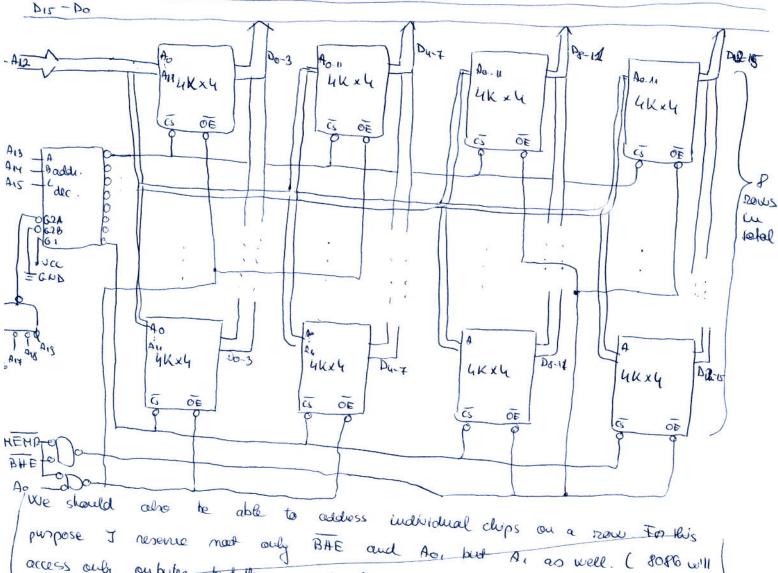

63. EPPON memory interfoce design. 29

we need a total size of 64KB = 64K x 8 bits, we have 4K x4 bits

thips => we need  $\frac{64K \times 8}{4K \times 4} = 16 \times 2 = 32$  thips

We have EPPOH, so we need to lete care only of the read operations,

as unite aperations does not occur.

For the POPG we have a 16 bit data bus. For this reason, we have to comect 4 such clips in a now to ensure this width. I In fact it will be parallel connection, because, even though the width is enlayed, should use reparate control lives for accessing low and high bytes).

dala bus

purpose I reserve most only BAE and Ao, but A, as well. ( 8086 will access only on bytes, but the conect designe teres into account this foresterne os,

We have 4K Hoors. Then we need 12 address lives to address the contents of a block. We use A - Ap for this purpose. Other address lines I such as ANG- Ag ) are designed, so that the memory is in the lower part of the address space. (Thus, these should be 0). The address-lines A13-A15 are used to nebot the rows.

So: 40 and BHE are used to select low I will byte or all would. A, - A,2 are used fraddessy uside one block of 4K.

A13-15 - used for addusting the 8 nows.

A16-15 - set 60. ( to map into tower part of memory).

For relating tow band we activate to (active tow) be high band BHE, for both we oclivate both. In addition we need the HEHD contail signe which Comes from MITO and RD:

For Low bowl the OE signed is corrected to:

For light brus OE is comested to Noto: 8086 will address only bytes. But in the hypertetical cose that we want to access the bands (all 4 colleurs) separately we use AOA, and BHE for soluting the High I low book as before and A, for nebelig the 4 bits in the byte, and the other addresses me slifted (i.e. we we Az. Ais and Am. Ais for addressing blocks and for decading nows.)

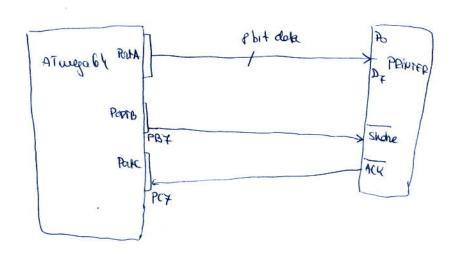

GI We need an I bit port for sending date, and a two contral lines: the STB and ACK. Because these are different directions (STB out, octin) I will use separate ports for Heur, although we would use the same post, with different ports configured differently. For the correct commication we madice that we should use latches for output parts and three-slet biffer for input ports PORTA will be the date port, PORTB will be for chabe, and PORTC for acrowinded we should make that in one of ATHORAG4 the Ports have beleviously their registers (in fact, every pin has its D flip-flap) So we do not need latches for output ports and three state buffers for input ports, as those effects are done automotically by the shuckene

af the port of an ATmopoler). The schematic will be then: ( mext page) DDR BUS -4-

2,5/

-> this is the schematic of a port, we can see that we have flipfleps for Portx, DDRx and have a three state buffer for the PINX, so we do not need to explicitly inhadice these who the design (ats it would be the case what using posts.)

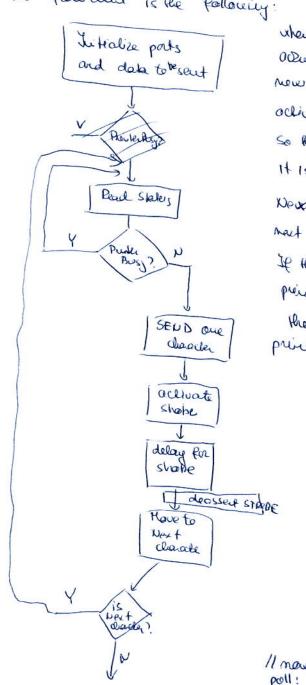

the flow chart is the following:

when the printer is busy we poll (wait for the orderentedge to be low i.e. -data was read, and now date can como.) We rend the date, and octivate shoke signal. We wait for some time so that shoke is Thead by printer (we how that it is not busy, so it should be a little amount). Nouse we dessent shope, and was move to the ment character. If we next character, we are done. If there is a next darock, read again status of the printer and loop

the assembly language program will be lite: print:

ldi 116, OXFF out BARA, 116 11 A part as output out DDRB, 116 11 B port as output ld 116,0x00 out DDPC, 216 Il port c as input.

Edi Xh, high (2\* string address) ld Xe, low (2x shingaddiess) // local inte x the address of the string to be ldi 1714, charcount widen 11 love to nix Re

number of characters.

the procedure itself 11 now poll :

in 1518, binc 11 med Boot pin C 5bc 218,7 11 step if bit I is cleared i.f. simp poll ACK ochève.

I now printer needy, send data Id NOO, X I load how weway the charecter. OUT POPTA, 220 11 send characte. ldi 1218, 0x 100 OUT POPTB, 1218 11 out the shale culie or low · lai 219,0x77 delay: dec orly Cpi 719,0 / delay loop brue delay ldi rill, 0x70 } deosset shope. ADDI XI, OXOI Red 2 B, O ADC Xh, nit DEC 214 // docement charety coul cbi vix,0 brone poll // of was saw, poll again net - if it was seen, neturn.

(the 16 bit time!)

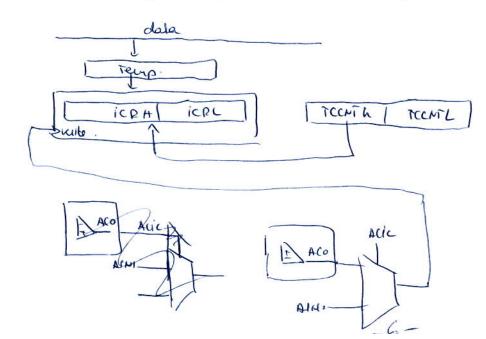

G2 the AVR Timer has a function called input capture. In this case

the contents of the oregister TCCNTM will be soved in 12C whenever an

input capture interrupt is requested. This is used for measuring frequencies,

periods or other analy characteristics of a signal. It is used in conjuction

with the analog comparator. The following is the aphabition:

The analog comparator compares the signals that are net by the ACBG and ACHE signels. ( AINO combe releval or Boudgop, AINI combe estuel or ADO-7). If the ACIC is set in the ACSR register (Analy comparetor Time cepture intempt enoble.), ou a modele (A(O) a time cepture intempt is reguested. This is the intempt of the Timen (16 bit timen) that can be validated in TiMSK register. When the intempt is requested, represent, the value of ICCNT register is put into the ICR register and ISR is called. France the substantine we can read the value and use if for some

Ex: measuring Requery or even measuring capacity of a condense:

the measuring aports of condenses:

1. configure timer and comparator.

2. Let PB3 be output and wito O to it to discharge the conderser

3. let PB3 be input (just like PB2)

4. start limer

S. On the isp.

- read icri

- convert to seconds

- calculate capacity using the characteristic equations of an RC low pass

|  |  |  | DE: |

|--|--|--|-----|

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |

|  |  |  |     |