## MICROPROCESSOR SYSTEMS (µP 2)

#### **GOAL:**

#### **PC Hardware Study:**

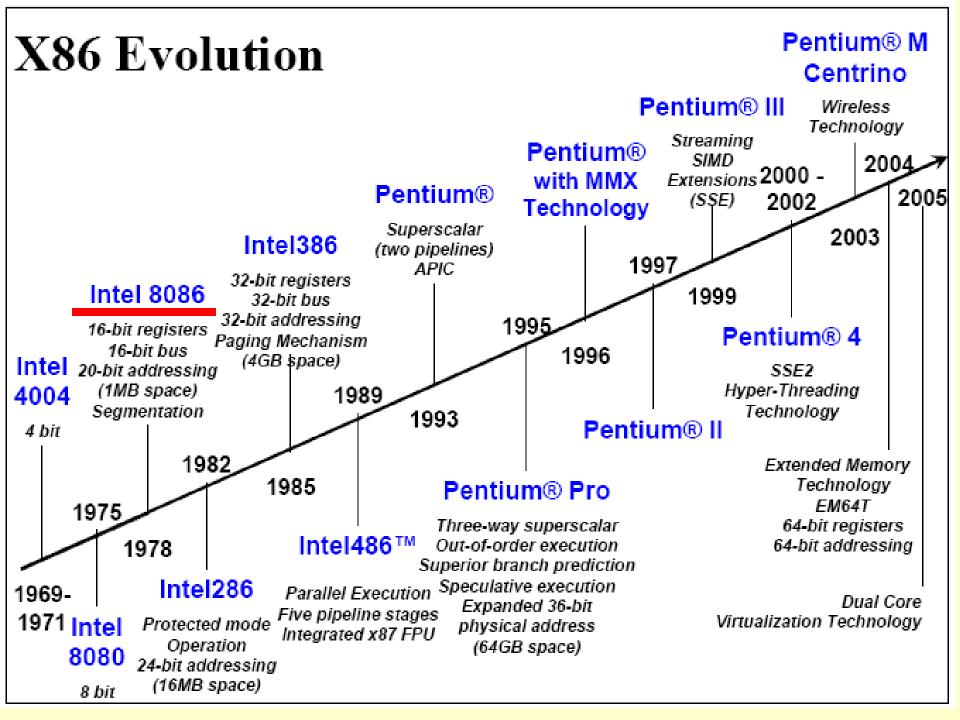

- -8086, Pentium

- Memory (Main, Cache)

- -Programmable Interfaces (Timer, PIC, DMAC, PIO) (architecture, programming, applications)

- SPP/EPP/ECP, COM, USB, I2C/SPI

- Buses (ISA, PCI)

#### REFERENCES

- -Lupu, E., Mesaroş, A., Suciu, A.F. MICROPROCESSORS. Architectures and Applications Ed. RISOPRINT Cluj-Napoca 2002

- -Lupu, E. SISTEME CU MICROPROCESOARE. Resurse hardware. Prezentare, programare şi aplicaţii. Ed. Albastră Cluj Napoca 2004, ISBN 973-650-109-4

- -Tischer M., Jennerich B. "LA BIBLE PC" PROGRAMMATION SYSTEME. MICRO Application 2003

- -Sztojanov, I. şi col. De la poarta TTL la Microprocesor (vol. II) Ed. TEHNICĂ

- -Buchanan, W. *PC interfacing, Communications and Windows Programming* Addison Wesley 1999

- -N. Mathivanan Microprocessors, PC Hardware and Interfacing PHI Learning Pvt. Ltd., 2003 ISBN 8120323173, 9788120323179 .....

- -www.pcguide.com, www.intel.com ,.....

- **SLIDES:** <a href="http://users.utcluj.ro/~elupu/Curs/index.php">http://users.utcluj.ro/~elupu/Curs/index.php</a>

#### **Evaluation:**

#### Final Mark

- 70% exam (theory + problems)  $\geq$  4.5

- 30 % laboratory tests ≥4.5

#### **BONUS:**

- Course attendance >50% roundup final mark else rounddown

- Homework +PRJ

" Life is hard, especially if you're stupid. " John Wayne

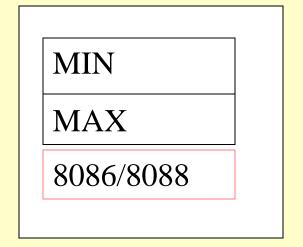

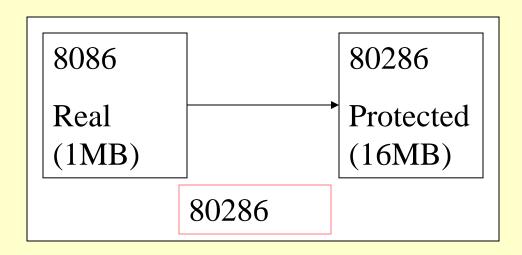

# C1 8086/88 MIN/MAX MODES

#### **OUTLINE**

- 8086/88 MIN/MAX modes

- Pin out

- Microsystems using 8086/88 in minimum mode

- 8284 Clock Generator

- 8086 timing

- Microsystems using 8086/88 in maximum mode

- Bus Controller 8288

| nal Data  | 16    | 8     | 16    | 32        | 32          | 64       | 64                          | 64                          | 64                          | 64                   |     |

|-----------|-------|-------|-------|-----------|-------------|----------|-----------------------------|-----------------------------|-----------------------------|----------------------|-----|

| Туре      | 8, 16 | 8, 16 | 8, 16 | 8, 16, 32 | 8,16,<br>32 | 8,16, 32 | 8, 16, 32                   | 8, 16, 32                   | 8, 16, 32                   | 8, 16, 32            |     |

| e<br>lory |       |       |       |           | 8 ko L1     | 16 ko L1 | 16 ko L1<br>256/512ko<br>L2 | 32 ko L1<br>256/512ko<br>L2 | 32 ko L1<br>256/512ko<br>L2 | 20 ko L1<br>512ko L2 | + 2 |

|           |       |       |       |           |             |          |                             |                             |                             |                      |     |

100

8086

1978

5-10

29 k

1 Mo

16

0.8

Year

no.

Bus

Extern Bus

Data 1

Cache

Memo

MIPS~

CLK (MHz)

**Transistors**

**Physical**

Memory

**Internal Data**

8088

1979

5-8

2 k

1 Mo

16

0.8

80286

1982

6-16

130 k

16 Mo

16

2.7

80386

1985

16-33

275 k

4 Go

**32**

6

80486

1989

25-50

1.2 M

4 Go

**32**

20

**Pentium**

1992

60/66

3.1 M

4 Go

32

**Pentium**

Pro

1995

150

5.5 M

64 Go

**32**

440

**Pentium**

Ш

1997

400

7.5 M

64 Go

32

440

**Pentium**

Ш

1999

800

28 M

64 Go

32

700

Pentium 4

2001

1700

42 M

64 Go

32

**P4 EE**

2004

3200-

3400

55M

2Mo

L3

13000

3000

# General features of Intel processors on 16/32 bits used in PCs

5

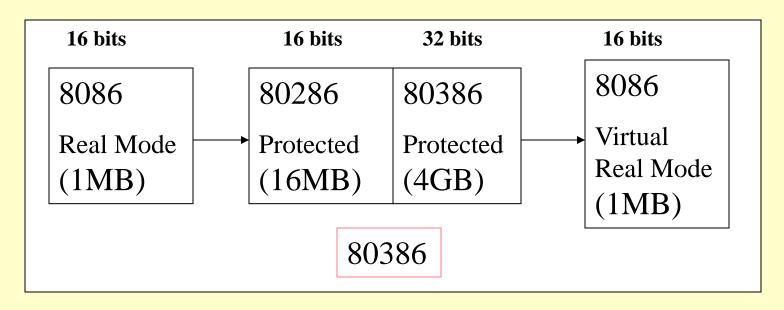

#### 8086 CPU

MIN MODE (MAX MODE)

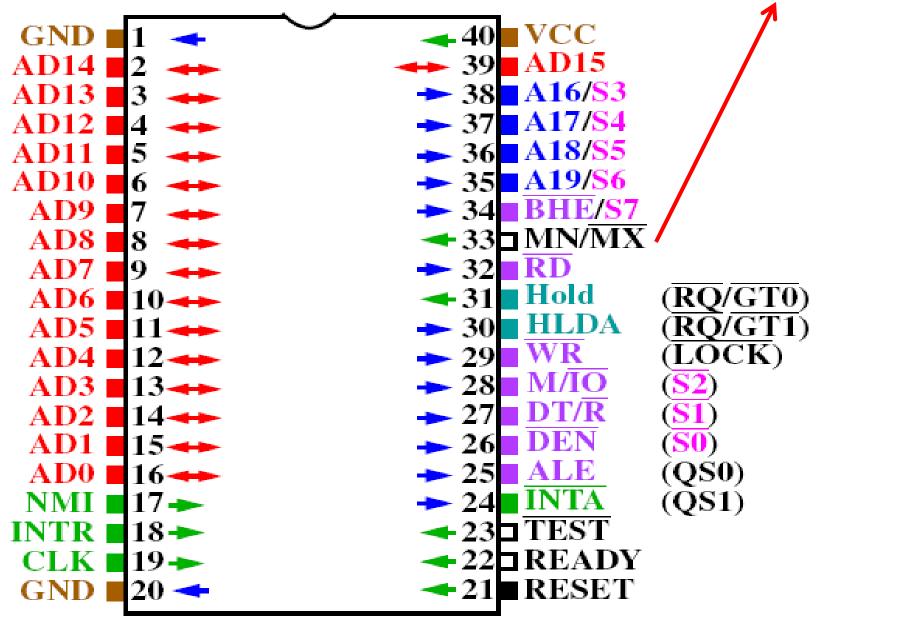

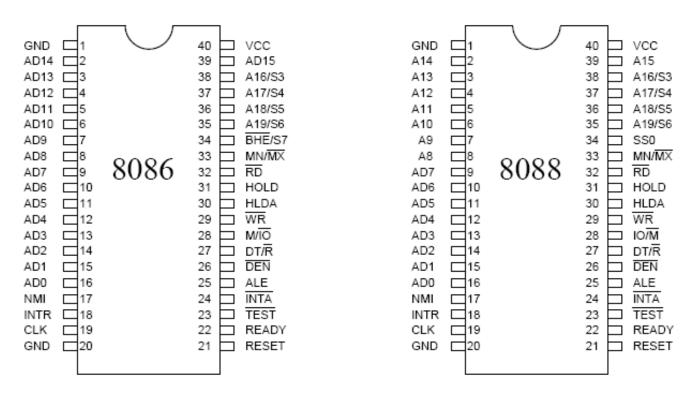

### 8086/8088 Pinout Diagrams

|     | 8086       |                                 |     | 8808       |                |  |

|-----|------------|---------------------------------|-----|------------|----------------|--|

| Pin | Mo         | ode                             | Pin | Mode       |                |  |

|     | Minimum    | Maximum                         |     | Minimum    | Maximum        |  |

| 31  | HOLD       | RQ/GT0                          | 31  | HOLD       | RQ/GT0         |  |

| 30  | HLDA       | RQ/GT1                          | 30  | HLDA       | RQ/GT1         |  |

| 29  | WR         | LOCK                            | 29  | HLDA<br>WR | LOCK           |  |

| 28  | M/IO       | <u>\$2</u><br><u>\$1</u><br>\$0 | 28  | IO/M       | S2<br>S1<br>S0 |  |

| 27  | DT/R       | S1                              | 27  | DT/R       | S1             |  |

| 26  | DEN        | SO                              | 26  | DEN        | <u>S0</u>      |  |

| 25  | <u>ALE</u> | QS0                             | 25  | ALE        | QS0            |  |

| 24  | INTA       | QS1                             | 24  | INTA       | QS1            |  |

|     |            |                                 | 34  | SS0        | High State     |  |

<sup>\*</sup>Minimum/Maximum Mode Refers to the Bus Handshaking

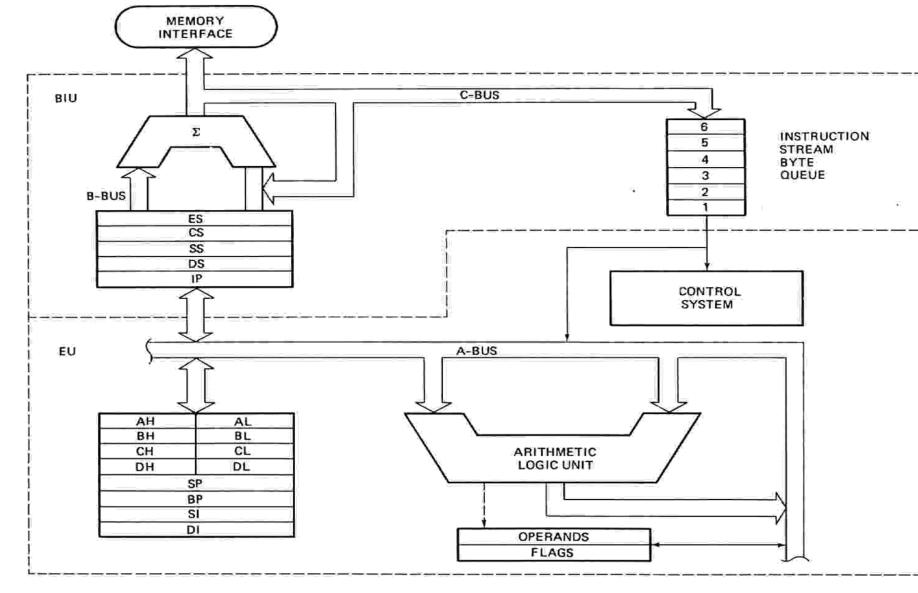

FIGURE 2-7 8086 internal block diagram. (Intel Corp.)

#### OAD15-AD0

### **8086 Pinout Signals**

Multiplexed address(ALE=1)/data bus(ALE=0).

OA19/S6-A16/S3 (multiplexed)

High order 4 bits of the 20-bit address OR status bits S6-S3.

$\bigcirc M/\overline{IO}$

Indicates if address is a Memory or IO address.

$\bigcirc RD$

When 0, data bus is driven by memory or an I/O device.

$\bigcirc \overline{WR}$

Microprocessor is driving data bus to memory or an I/O device. When 0, data bus contains valid data.

OALE (Address latch enable)

When 1, address data bus contains a memory or I/O address.

○DT/R (Data Transmit/Receive)

Data bus is transmitting/receiving data.

ODEN (Data bus Enable)

Activates external data bus buffers.

$\bigcirc$  S7, S6, S5, S4, S3,  $\overline{S2}$ ,  $\overline{S1}$ ,  $\overline{S0}$

**S7**: Logic 1, S6: Logic 0.

S5: Indicates condition of IF flag bits.

**S4-S3**: Indicate which segment is accessed during current bus cycle:

| S4 | S3 | Function           |

|----|----|--------------------|

| 0  | 0  | Extra segment      |

| 0  | 1  | Stack segment      |

| 1  | 0  | Code or no segment |

| 1  | 1  | Data segment       |

$\overline{S2}$ ,  $\overline{S1}$ ,  $\overline{S0}$ : Indicate function of current bus cycle (decoded by 8288).

| <u>S2</u> | <u>S1</u> | <u>S0</u> | Function      |   | S2 | S1 | <del>S</del> 0 | Function     |

|-----------|-----------|-----------|---------------|---|----|----|----------------|--------------|

| 0         | 0         | 0         | Interrupt Ack |   | 1  | 0  | 0              | Opcode Fetch |

| 0         | 0         | 1         | I/O Read      |   | 1  | 0  | 1              | Memory Read  |

| 0         | 1         | 0         | I/O Write     |   | 1  | 1  | 0              | Memory Write |

| 0         | 1         | 1         | Halt          | • | 1  | 1  | 1              | Passive      |

#### $\bigcirc$ *INTR*

When 1 and IF=1, microprocessor prepares to service interrupt. INTA becomes active after current instruction completes.

#### O INTA

Interrupt Acknowledge generated by the microprocessor in response to INTR. Causes the interrupt vector to be put onto the data bus.

#### ONMI

Non-maskable interrupt. Similar to INTR except IF flag bit is not consulted and interrupt is vector 2.

#### O CLK

Clock input must have a duty cycle of 33% (high for 1/3 and low for 2/3s)

#### O VCC/GND

Power supply (5V) and GND (0V)

### $\bigcirc MN/\overline{MX}$

Select minimum (5V) or maximum mode (0V) of operation.

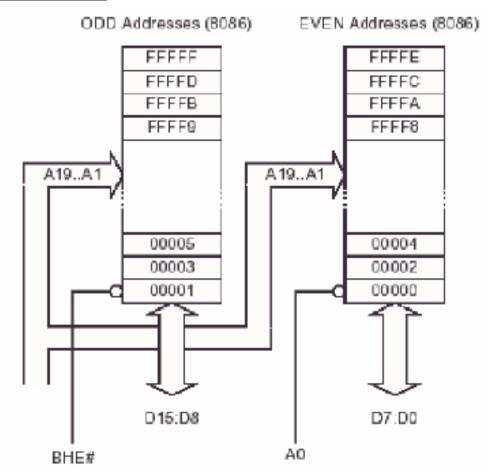

#### ) BHE

Bus High Enable. Enables the most significant data bus bits  $(D_{15}-D_8)$  during a read or write operation.

#### ○ READY

Used to insert wait states (controlled by memory and IO for reads/writes) into the microprocessor.

#### ○ RESET

Microprocessor resets if this pin is held high for 4 clock periods.

Instruction execution begins at FFFF0H and IF flag is cleared.

#### O TEST

An input that is tested by the WAIT instruction.

Commonly connected to the 8087 coprocessor.

#### $\bigcirc$ *HOLD*

Requests a direct memory access (DMA). When 1, microprocessor stops and places address, data and control bus in high-impedance state.

#### ○ *HLDA* (Hold Acknowledge)

Indicates that the microprocessor has entered the hold state.

# **✓BHE (Bank High Enable) line** (8086 only) :=0 for most significant byte of data and also carries $S_7$ =1

| BHE# | A0 | Selection                     |

|------|----|-------------------------------|

| 0    | 0  | Whole word (16-bits)          |

| 0    | 1  | High byte to/from odd address |

| 1    | 0  | Low byte to/from even address |

| 1    | 1  | No selection                  |

### $\bigcirc RO/GT1$ and RO/GT0

Request/grant pins request/grant direct memory accesses (DMA) during maximum mode operation.

### $\bigcirc \overline{LOCK}$

Lock output is used to lock peripherals off the system. Activated by using the LOCK: prefix on any instruction.

### ○QS1 and QS0

The queue status bits show status of internal instruction queue. Provided for access by the numeric coprocessor (8087).

- O Clock generation 6204 CLOCK GENERATION

- RESET synchronization

- O READY synchronization

- O Peripheral clock signal

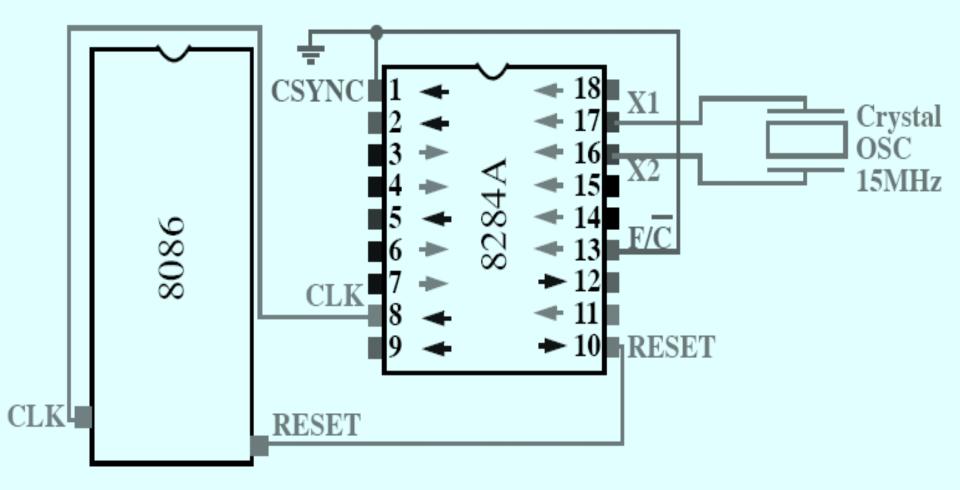

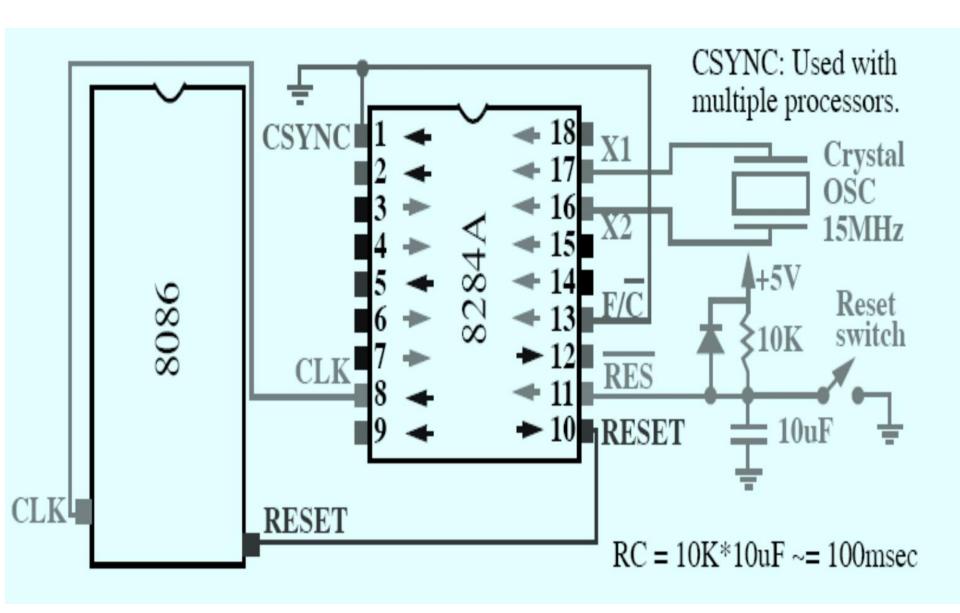

Connection of the 8284 and the 8086.

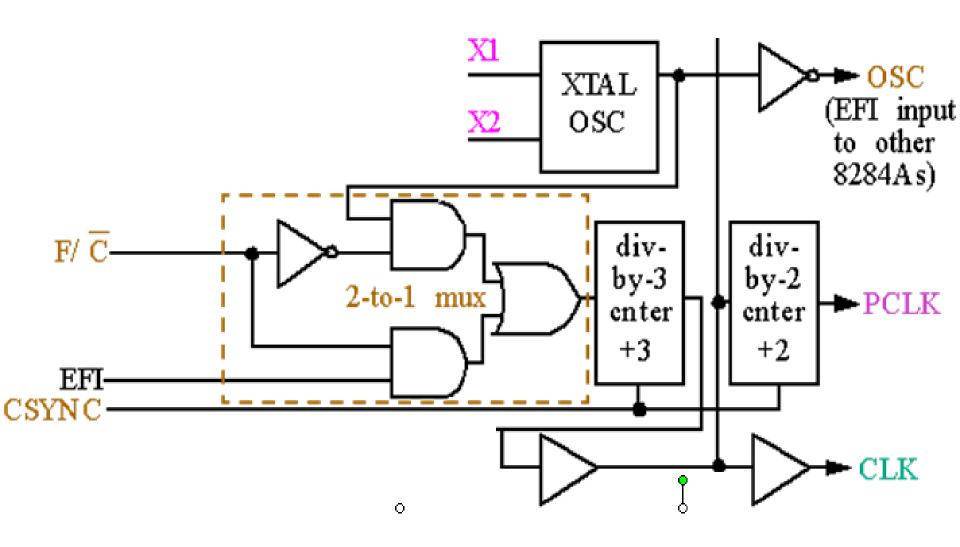

**Block diagram of the 8284**

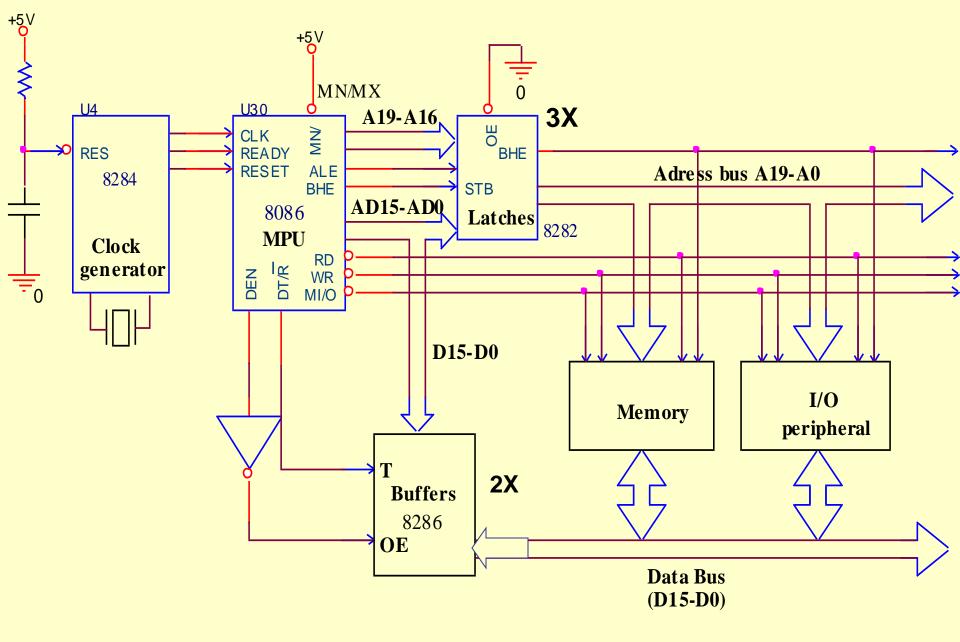

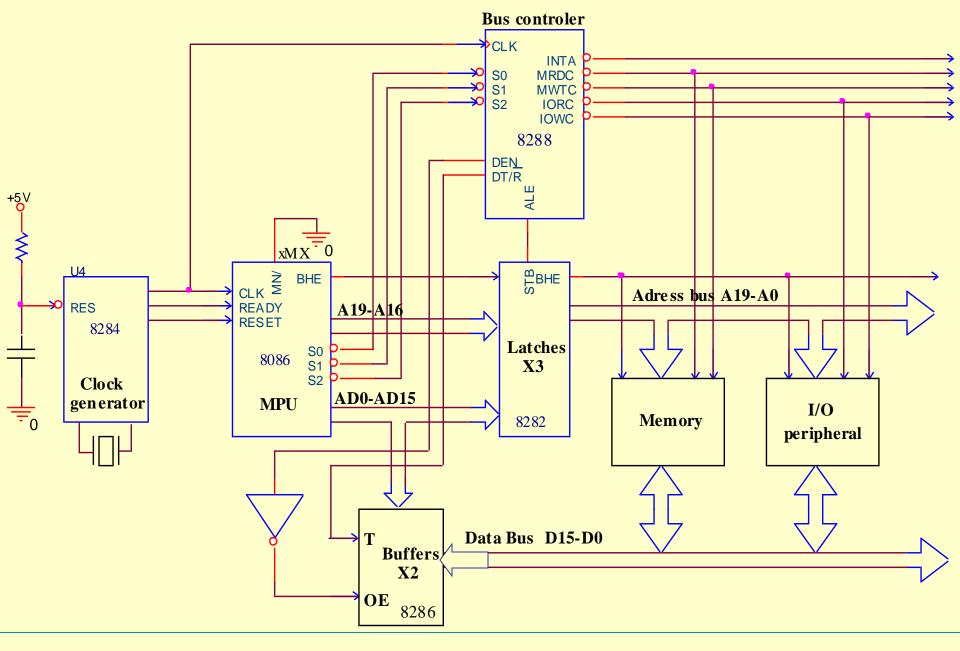

Microsystem using 8086 in minimum mode

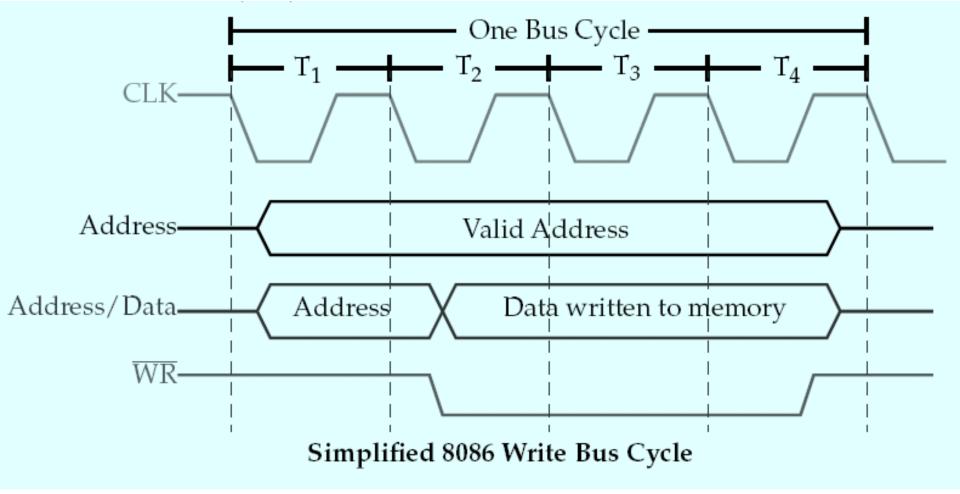

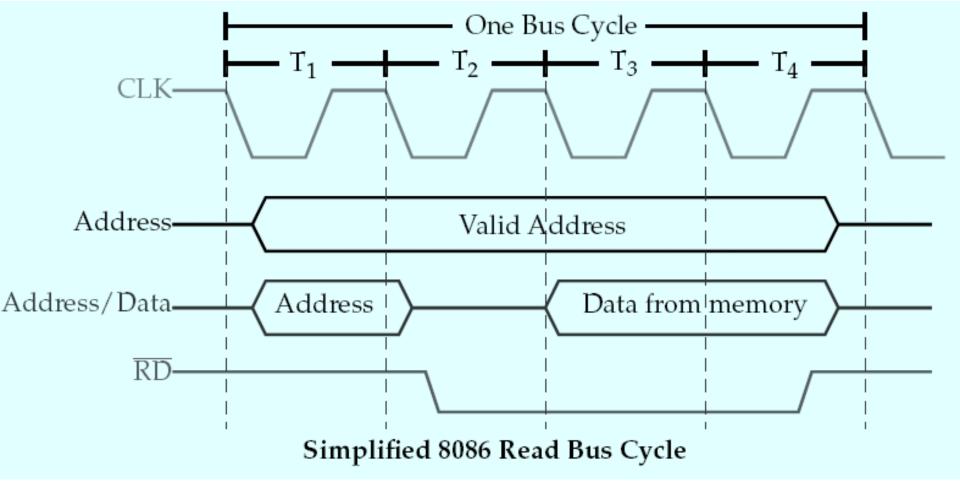

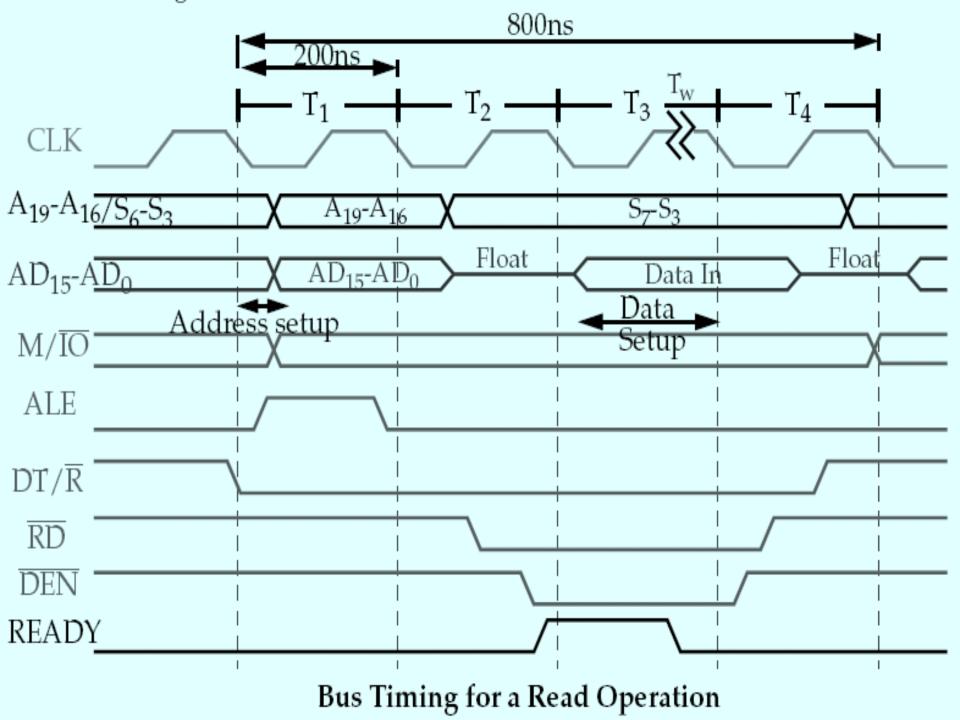

### **Bus Cycle and Time States**

- T1 start of bus cycle. Actions include setting control signals (or S0-S2 status lines) to give the required values for ALE, DTR IO/M putting a valid address onto the address bus.

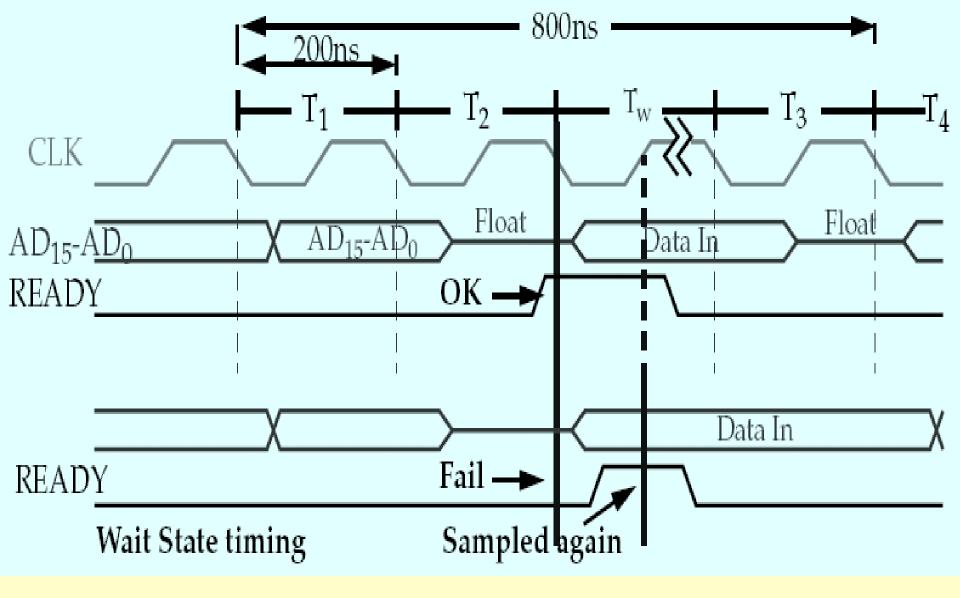

- T2 the RD or WR control signals are issued, DEN is asserted and in the case of a write, data is put onto the data bus. The DEN turns on the data bus buffers to connect the CPU to the external data bus. The READY input to the CPU is sampled at the end of T2 and if READY is low, a wait state  $T_W$  (one or more) is inserted before T3 begins.

- T3 this clock period is provided to allow memory to access the data. If the bus cycle is a read cycle, the data bus is sampled at the end of T3.

- T4 all bus signals are deactivated in preparation for the next clock cycle. The 8088 also finishes sampling the data (in a read cycle) in this period. For the write cycle, the trailing edge of the WR signal transfers data to the memory or I/O, which activates and write when WR returns to logic 1 level.

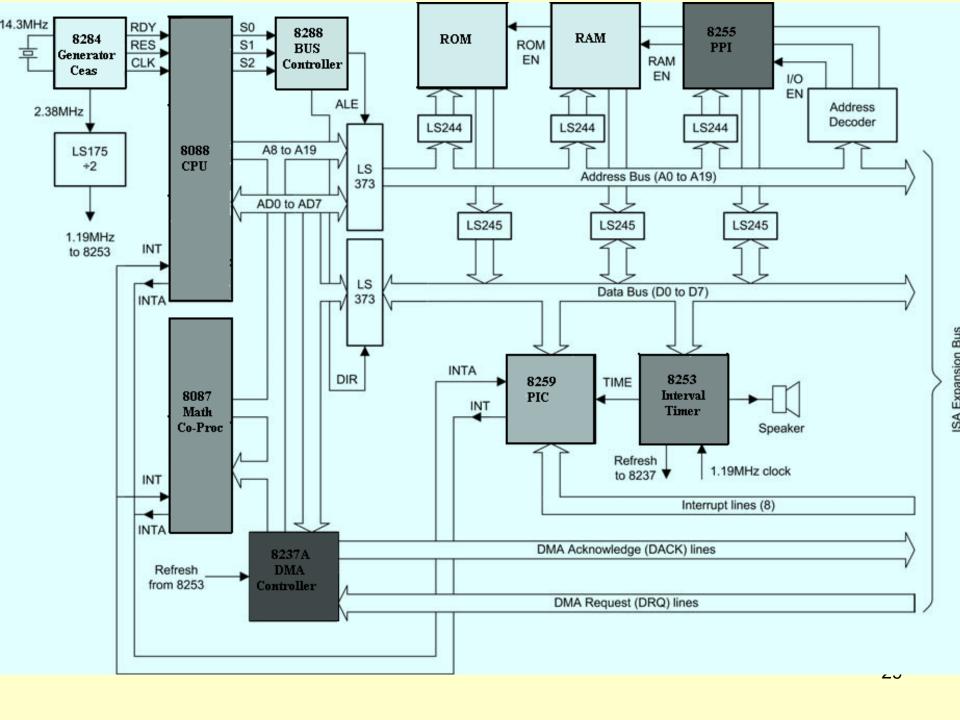

Microsystem using 8086 in maximum mode

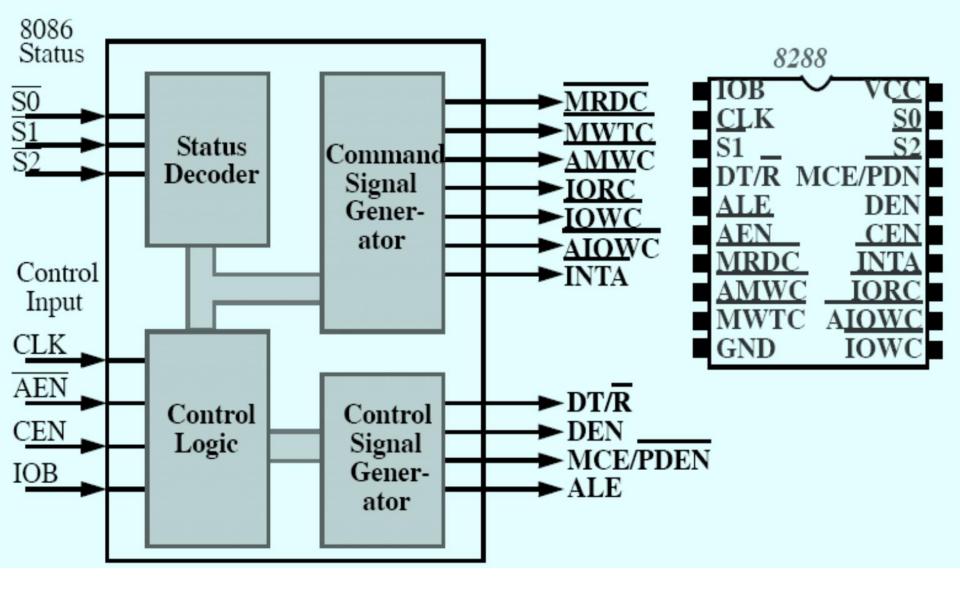

Block diagram of the 8288 Bus Controller

#### MAX Mode 8086 System S0 S1 S2 CLK 8284A RES MRDC READY RESET 8288 IORC 8086 ALÉ **CPU** STB Address $AD_0$ - $AD_{15}$ Latches INT Data ÓΕ 8286 Transceiver WR RD 8259A

IRQ 0-7

**RAM**

Interrupt

Controller

### **8086 interview questions**• What are the flags in 8086? - In 8086 Carry flag, Parity flag, Auxiliary carry flag, Zero flag, Overflow flag, Trace flag,

•What is Non-Maskable interrupts? - An interrupt which can be never be turned off (ie.disabled) is known as Non-Maskable interrupt.

•What is meant by Maskable interrupts? - An interrupt that can be turned off by the programmer is known as Maskable

•Which interrupts are generally used for critical events? - Non-Maskable interrupts are used in critical events. Such as Power failure, Emergency, Shut off etc.,

• Give example for Non-Maskable interrupts? - Trap is known as Non-Maskable interrupts, which is used in emergency

- condition.

- •What is the Maximum clock frequency in 8086? 5 Mhz is the Maximum clock frequency in 8086.

• What are the various interrupts in 8086? - Maskable interrupts, Non-Maskable interrupts.

Interrupt flag, Direction flag, and Sign flag.

- •What are the various segment registers in 8086? Code, Data, Stack, Extra Segment registers in 8086.

- •Which is the tool used to connect the user and the computer? Interpreter is the tool used to connect the user and the tool.

- •What is the position of the Stack Pointer after the PUSH instruction? The address line is 02 less than the earlier value.

- •Logic calculations are done in which type of registers? Accumulator is the register in which Arithmetic and Logic calculations are done.

•What is the position of the Stack Pointer after the POP instruction? - The address line is 02 greater than the earlier value.

- •What are the different functional units in 8086? Bus Interface Unit and Execution unit, are the two different functional

- units in 8086.

•What is meant by cross-compiler? A program rups on one machine and executes on another is called as cross-compiler.

- •What is meant by cross-compiler? A program runs on one machine and executes on another is called as cross-compiler.

•Which Segment is used to store interrupt and subroutine return address registers? Stack Segment in segment register is

- used to store interrupt and subroutine return address registers.

Which Flags can be set or reset by the programmer and also used to control the operation of the processor? Trace Flag,

- Interrupt Flag, Direction Flag.

What does FU do? Execution Unit receives program instruction codes and data from BUL, executes these instructions and

- •What does EU do? Execution Unit receives program instruction codes and data from BIU, executes these instructions and store the result in general registers.

- •Which microprocessor accepts the program written for 8086 without any changes? 8088 is that processor. 30

•What is the difference between 8086 and 8088? The BIU in 8088 is 8-bit data bus & 16- bit in 8086.Instruction queue is 4 byte long in 8088and 6 byte in 8086.